ECB-Bus beim GENIE 1 und 2

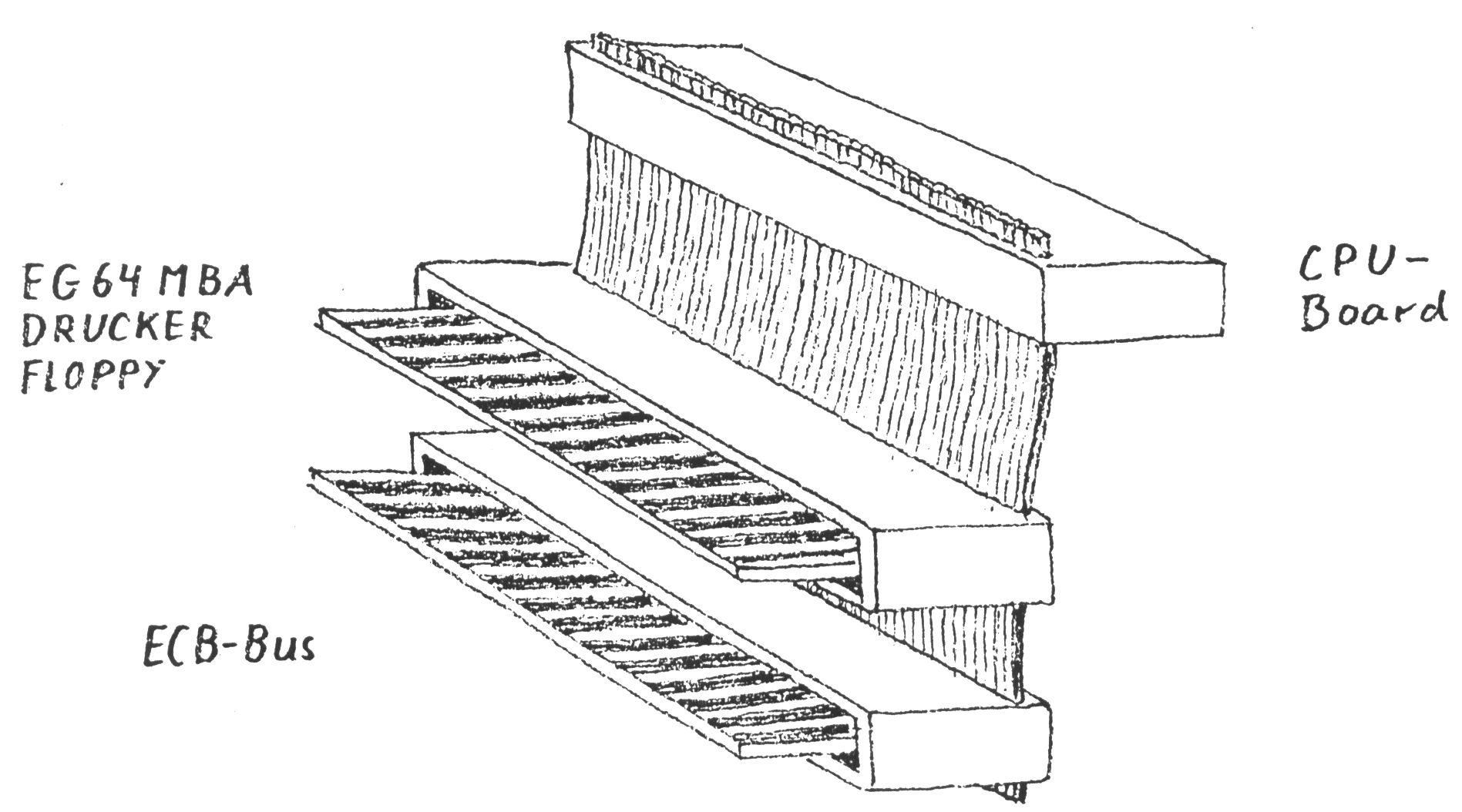

Helmut BernhardtSoweit allgemein bekannt ist, gibt es für den direkten Anschluß an den Systembus des GENIE lediglich das alte Expansion-Interface EG3014 mit 32K RAM und den Interfaces für Floppy und Drucker oder später dann den Floppy-Controller im Laufwerksgehäuse (der wegen seines langen Kabels kapazitiv unnötig belastet). Außerdem ist noch der Kleinkram wie EG64MBA und eine emtsprechende Centronics- Schnittstelle zu erwähnen. Das war's dann wohl schon.

Wenn man sich nun nicht alle offenstehenden Wünsche mit dem Lötkolben selbst realisieren will, sondern auf das reichhaltige Angebot fertiger Karten für Z80- Computer zurückgreifen möchte, ist es zweckmäßig, sich eine ECB-Bus-Platine zu kaufen und diese über eine Steckverbindung an den Systembusstecker des GENIE anzuschließen. Der ECB-Bus ist der bei Z80-Systemen am meisten verbreitete Busstandard, für den es alle beliebigen Systemerweiterungen zu kaufen gibt.

Dabei ist allerdings abzusehen, daß das Fanout der Treiber der Z80-Signale nicht unendlich ist und die Anzahl der auf dem ECB-Bus angeschlossenen Karten begrenzt ist (besonders dann, wenn die Floppystation über ein unverschämt langes Buskabel angeschlossen ist). Deshalb soll demnächst auch noch eine Steuerkarte für einen gepufferten ECB-Bus vorgestellt werden, die trotz Pufferung auch noch IM2- und DMA-Fähigkeit aufrechterhält.

Bei der Untersuchung der Pinbelegung des ECB-Bus <1> erkennt man die meisten Signale des GENIE-Systembus wieder. Solche Signale können einfach vom GENIE-Bus abgegriffen werden und auf den entsprechenden Pin des ECB-Bus gelegt werden (D0-D7, A0-A15, RD*. WR*, MERQ*, IORQ*, RESET*, NMI*, INT*, RFSH*, HALT*, M1*, WAIT*, BUSREQ*, BUSAK*, CLOCK, +5V, GND).

Weitere Signale spielen für den GENIE keine Rolle. Sie bleiben am ECB-Bus unberücksichtigt (PWRCL*, VCMOS, ext.RFSH*, +15V, und bei einigen Varianten auch noch -15V, A16-A19).

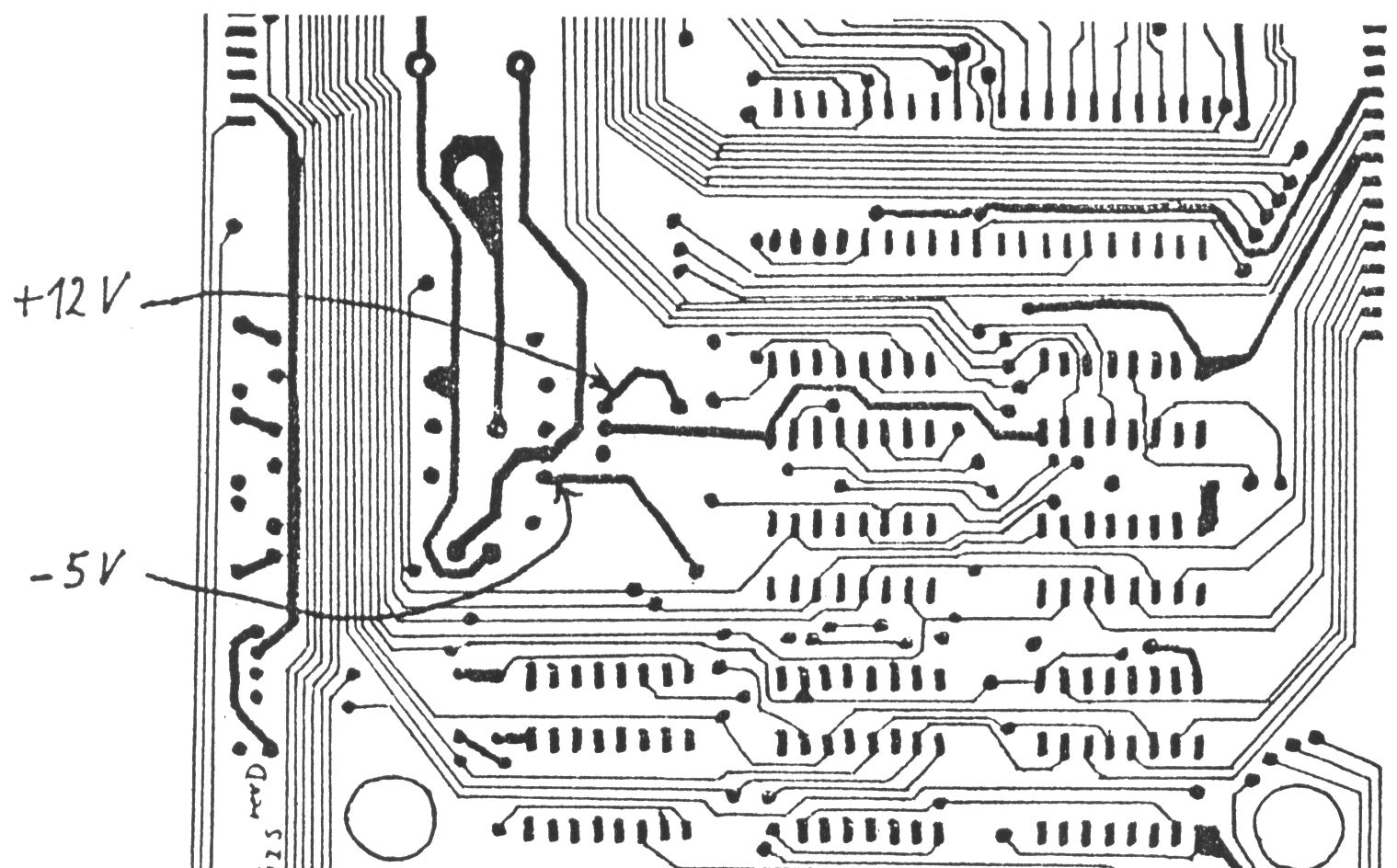

Abb.1: Abgreifen der Versorgungs-Spannungen +12V und -5V auf dem CPU-Board

Abb.1: Abgreifen der Versorgungs-Spannungen +12V und -5V auf dem CPU-BoardDie Signale IN* und OUT* liegen nicht auf dem GENIE-Bus, sie müssen an den Pins 32 und 31 des Verbindungssteckers zum Video-Inteface abgegriffen werden. Auch die Versorgungsspannungen +12V und -5V müssen bei Bedarf auf dem CPU- Board an den in Abb.1 bezeichneten Stellen entnommen und gesondert an den ECB-Bus geführt werden.

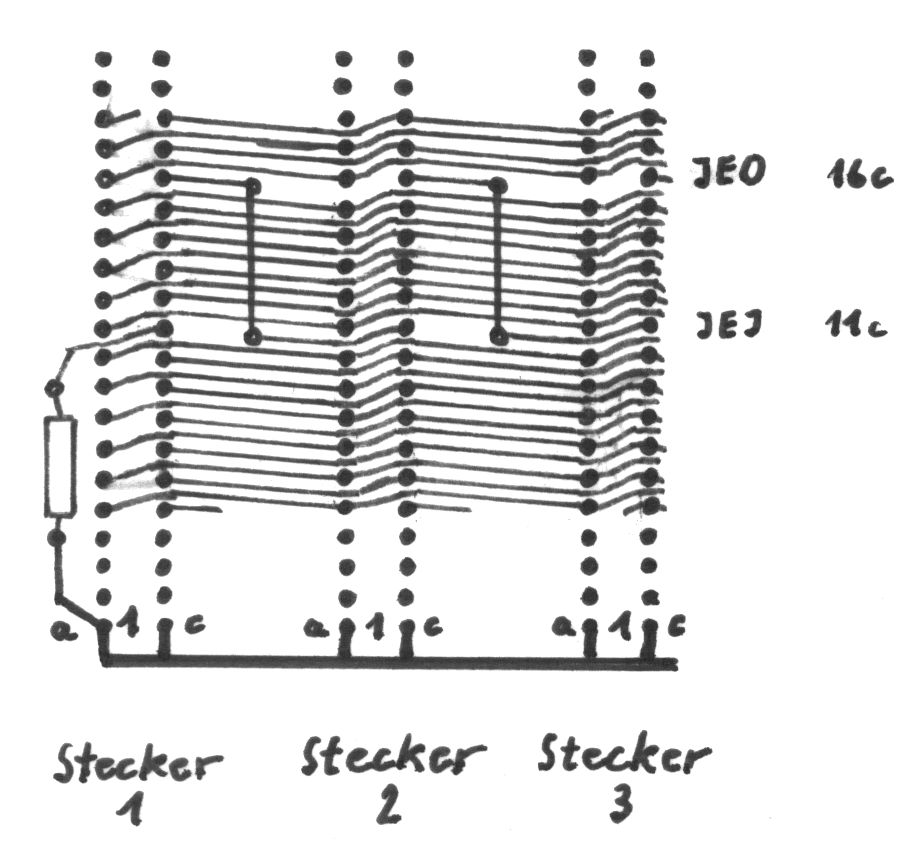

Abb.2: IEI-IEO-Daisy-Chain auf dem ECB-Bus

Abb.2: IEI-IEO-Daisy-Chain auf dem ECB-BusEs bleiben auf dem ECB-Bus noch die Signale IEI und IEO übrig. Diese bilden die Interrupt-Daisy-Chain zwischen den einzelnen ECB-Bus-Karten. Auf der ECB- Busplatine sind diese Signale nicht von Stecker zu Stecker direkt miteinander verbunden. Es ist immer der Pin IEI (Interrupt Enable In) einer Steckkarte mit dem Pin IEO (Interrupt Enable Out) des Steckers davor verbunden, während der Pin IEO jeden Steckers mit dem Pin IEI des Steckers dahinter verbunden ist. Beim ersten Stecker ist der Pin IEI über einen Widerstand von einigen KOhm an +5V gelegt. Durch diese Busstruktur ist den einzelnen Steckplätzen (vom ersten zum letzten abfallend) ihre Interrupt Priorität zugeordnet.

Eine Karte kann der CPU nur dann einen Interrupt liefern, wenn der Eingang IEI der Karte high ist. Die Z80 Peripherie Bausteine verfügen über entsprechende Pins IEI und IEO. Ein Baustein, der gerade einen Interrupt gemeldet hat, gibt über IEO Low-Pegel aus und unterdrückt dadurch am Eingang IEI des nächsten angeschlossenen Bausteins einen eventuellen Interrupt. Ein Baustein, dessen IEI-Eingang auf Low geht, gibt diesen Pegel dann über seinen IEO-Ausgang an den nächsten Baustein weiter, so daß bei allen nachgeschalteten Bausteinen dadurch das Ausgeben eines Interrupts verhindert wird. Erst wenn der den Interrupt auslösende Baustein auf dem Datenbus die beiden Bytes des Befehls RETI nacheinander erkennt, nimmt er seinen IEO-Ausgang wieder auf High zurück und ermöglicht dadurch niedriger priorisierten Bausteinen, Interrupts an die CPU abzusetzen (vorausgesetzt, sein IEI-Eingang ist nicht durch einen Interrupt eines höher priorisierten Bausteins inzwischen auf Low gesetzt worden).

Während des Abarbeitens einer Interrupt-Service-Routine läßt sich die CPU nicht durch den Interrupt eines höher priorisierten Bausteins stören. Dieser wird erst angenommen, nachdem RETI ausgeführt wurde. Es kommt also nicht zur Verschachtelung von Interrupt-Routinen und dem dadurch verursachten Chaos auf dem Stack.

Auf ECB-Bus-Karten, die selbst keinen Interrupt auslösen können, sind die Pins IEI und IEO des Busteckers miteinander verbunden, so daß die Daisy-Chain nicht unterbrochen wird. Es dürfen auch aus diesem Grund zwischen zwei Karten keine leeren Stecker auf der Busplatine vorhanden sein.

Da die im GENIE üblichen Interrupt-Quellen (Timer, Floppy-Controller und

eventuell serielle Schnittstelle) diese Interrupt-Struktur nicht unterstützen,

müssen die Signale durch Verwendung eines Z80-CTC auf dem ECB-Bus in diese

Struktur eingebunden werden, wenn man den äußerst leistungsfähigen Interrupt-

Modus 2 nutzen will. Der Z80-CTC stellt ihnen dann auch einen Vektor für den

IM2 zur Verfügung <2;3>.

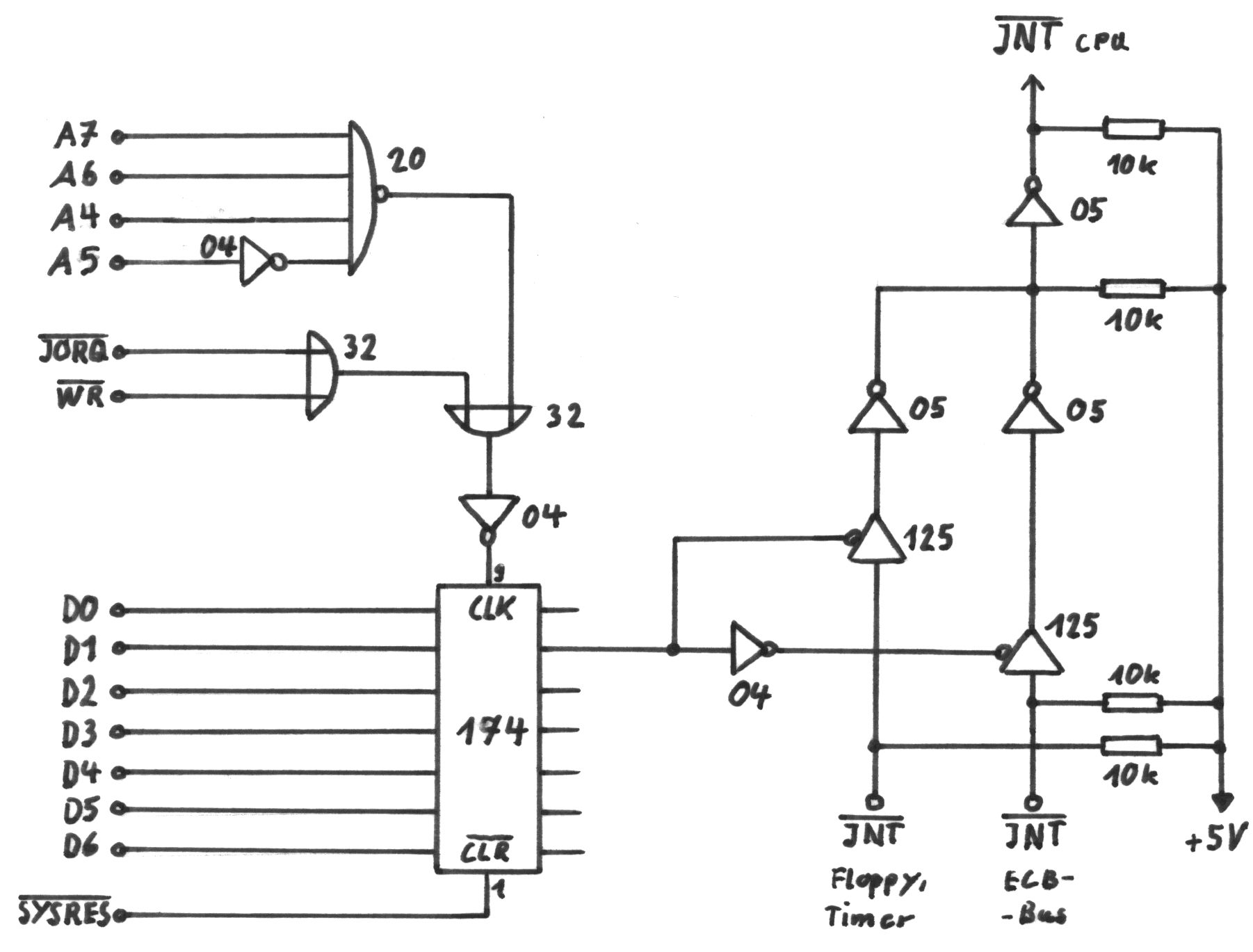

Abb.3: Programmierbare Umleitung des INT*-Signals von FDC und Uhr über

einen Z80-CTC-Kanal

Abgesehen vom eventuellen Interrupt einer seriellen Schnittstelle werden die Interrupt-Signale von Timer und FDC über eine gemeinsame Leitung an den INT-Pin der CPU geführt. Durch etwas Hardware (Abb.3) läßt sich über Software dieses Interrupt-Signal entweder direkt an die CPU führen oder über einen Z80-CTC Zählereingang umleiten, wobei dann der IM2 unterstützt wird. Da auch im Betriebssystem beide Interrupts von der gleichen Service-Routine bedient werden, reicht im IM2 auch ein Vektor eines CTC-Kanals aus. In der Interrupt- Tabelle darf aber nicht das Sprungziel 4012H stehen (Interrupt Vektor des IM1 des DOS), da die Interrupt-Service-Routine des DOS nicht mit RETI sondern mit RET endet und der Z80 dann nicht weiß, wann er seinen IEO-Ausgang wieder auf High zurücknehmen soll. Es muß folgender Umweg eingeschlagen werden:

INTTAB DEFW SERV1 ;ANFANG INTERRUPT TABELLE DÜR IM2 DEFW SERV2 ;VEKTOR FÜR DEN NÄCHSTEN INT-LIEFERANTEN DEFW .... ;U.S.W. .... DEFW CTC ;* SIEHE FUSSNOTE .... CTC CALL 4012H ;TIMER-, FLOPPY-INT.-ROUTINE EI RETI * Das Lable CTC ist der Anfang der Interrupt-Service-Routine für Timer und Floppy. Seine Adresse ist in der Interrupt- Tabelle an der Adresse eingetragen, deren höherwertiges Byte in das I-Register der CPU eingetragen worden ist und deren niederwertiges Byte dem entsprechende CTC-Kanal als Interrupt-Vektor einprogrammiert worden ist.

Schließlich bleiben noch die Signale CCDBS/STADBS* und DODBS/ADDBS* des GENIE-Bus übrig. Diese sind für den Betrieb eines externen DMA-Controllers vorgesehen.

Ein DMA-Controller <4;5> kann, wenn er von der CPU dazu aufgefordert wird, die Kontrolle über den Systembus übernehmen und selbst auf Speicher und Ports zugreifen. Dabei liefert er dann die Bussignale (außer natürlich beim Lesen die Signale D0-D7 selbst. Die Synchronisation mit der CPU erfolgt dadurch, daß der DMAC Low-Pegel auf die Leitung BUSREQ* legt, woraufhin die CPU dann als Quittung Low über den Pin BUSAK* ausgibt und ihre Daten-, Adreß- und Steuerpins in den hochmigen Zustand versetzt.

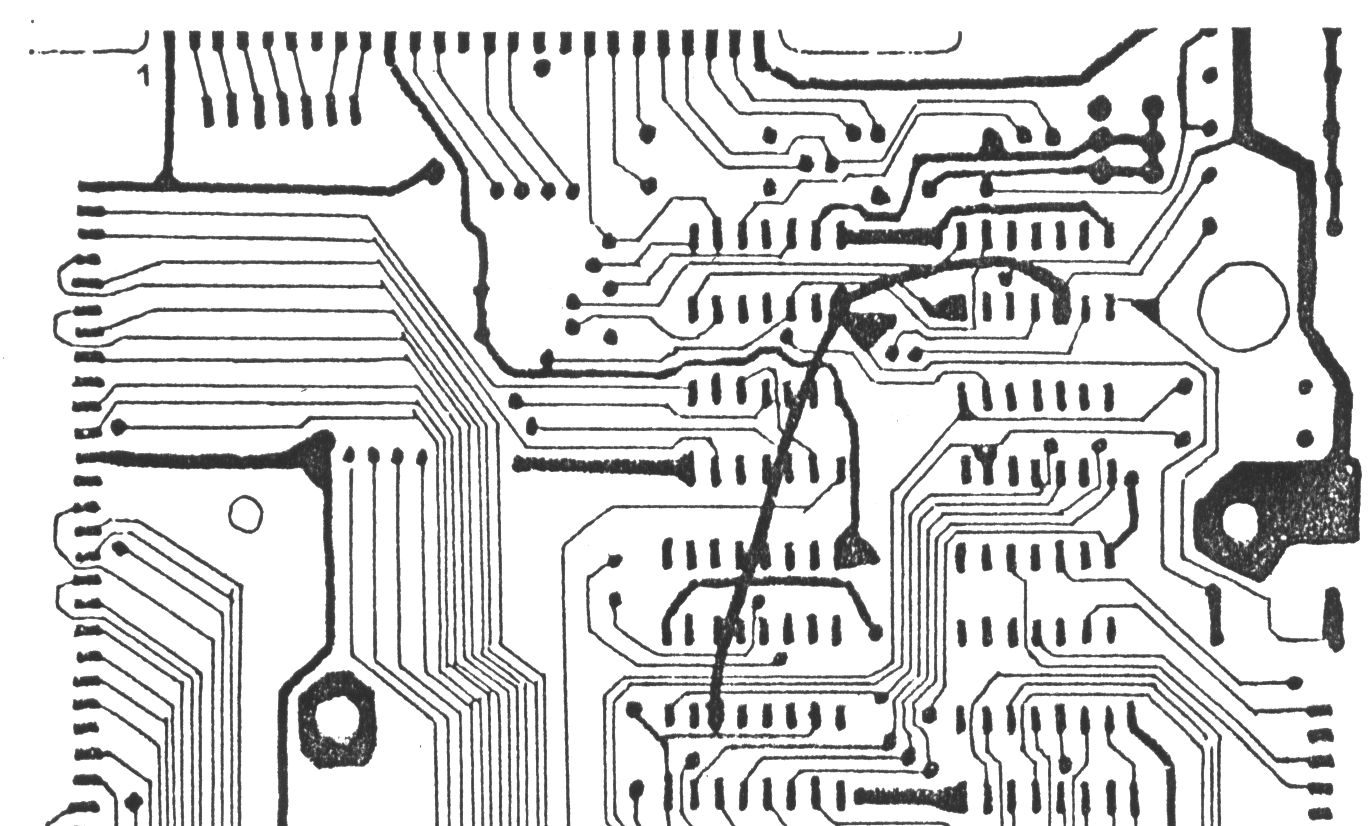

Abb.4: Anschließen des Signals BUSAK* an die Steuereingänge CCDBS/STADBS*

und DODBS/ADDBS* auf dem CPU-Board, Ansicht des CPU-Boards von der Lötseite

Abb.4: Anschließen des Signals BUSAK* an die Steuereingänge CCDBS/STADBS*

und DODBS/ADDBS* auf dem CPU-Board, Ansicht des CPU-Boards von der Lötseite

Es müssen auch die Treiber dieser CPU-Signale in den hochohmigen Zustand versetzt werden, damit deren Ausgänge nicht gegen die Signale des DMAC arbeiten. Die Freigabeeingänge dieser Treiber lassen sich über die Pins CCDBS/STADBS* und DODBS/ADDBS* steuern. Wenn diese Pins auf low gezogen werden, sperren die Treiber der CPU ihre Ausgänge so, daß dann der DMAC den Bus kontrollieren kann. Es muß also das Signal BUSAK* an diese Pins des GENIE-Bus gelegt werden (Abb.4). Diese Änderung kann auch bestehen bleiben, wenn kein ECB-Bus angeschlossen ist oder wenn kein DMA-Betrieb vorgesehen ist und auch sonst kein Gebrauch dieser Steuereingänge des GENIE-Bus gemacht wird, denn BUSAK* ist normalerweise immer high.

Unberücksichtigt bleibt das Signal PHANTOM*. Wenn dieser Pin des GENIE-Bus auf Low gezogen wird, so werden sämtliche Systemkomponenten im Adreßbereich 0 bis 3FFFH (ROM, Floppy, Drucker, Tastatur und Bildschirm) nicht mehr freigegeben und stattdessen RAM in diesem Bereich zur Verfügung gestellt. Eine gezielte Steuerung des PHANTOM*-Eingangs zum Banking leistet das EG64MBA und ein jüngerer Verwanter davon <6>.

Der Anschluß eines ECB-Bus an den GENIE-Systembusstecker ist am einfachsten, wenn dieser Stecker unbenutzt ist (z.B. Floppy-, Drucker-Interface von RB- Elektronic im Grundgetät). Bei angeschlossenem herkömmlichen Expansion-Interface EG3014 oder neuerer Floppy-Station mit internem Floppy-Controller sowie bei aufgestecktem Drucker-Interface oder EG64MBA treten Schwierigkeiten auf. Am güstigsten ist dabei eine Busweiche, d.h. ein kurzes Stück 50poliges Flachbandkabel mit 3 (oder mehreren) Quetschverbindungen gemäß Abb.5. Daran können dann ECB-Bus und alle anderen Systemkomponenten für den GENIE-Bus gleichzeitig betrieben werden. Um an diese Weiche wiederum die weiblichen Stecker der Peripherie-Geräte anschließen zu können, braucht man männliche Zwischenstücke (Platinenstücke mit beidseitig im 1/10 Zoll-Raster geätzten Streifen.

Es sei noch angemerkt, daß bei dem aus dem EG64MBA herausführenden Systembus das Signal MERQ* nicht das gleiche ist wie bei dem vom CPU-Board kommenden MERQ*. Dieses Signal ist schon mit dem Latch-Ausgang des MBA, der das Banking des Bereichs 3600H-37FFH steuert, verknüpft. Wenn dieser Bereich durch den entsprechenden MBA-Befehl als RAM eingestellt ist, bleibt der MERQ*-Ausgang des MBA ständig high, damit dann nicht der Floppy-Controller im Laufwerksgehäuse angesprochen wird.

Bei dem aufwärtskompatiblen Selbstbau-Banker aus <6> kann man sich das herausgeführte MERQ* entsprechend seiner Systemkonfiguration wählen. Wenn der Floppy-Controller nicht im Laufwerksgehäuse untergebracht ist, sollte dort das richtige MERQ* herausgeführt werden. Auch die Signale A14 und A15 sollten dann die des Systembus sein.

Das Prinzip des Anschlusses des ECB-Bus läßt sich auch auf TRS80 (nur Modell 1) und Komtek 1 übertragen. Beim Komtek müssen bei Einsatz eines CPU-Treiber-Boards <7> die Freigabe-Pins der Treiber (Pins 1 und 19 bei den ICs 74LS244 und nur Pin 19 beim 74LS245) mit dem über ein freies AND-Gatter auf dem 74LS00 dieses Boards invertierten BUSAK* der CPU verbunden werden und dürfen nicht wie bisher an GND liegen. Diese Änderung ist aber nicht nötig, wenn kein DMA-Betrieb vorgesehen ist. Der IM2-Betrieb ist bei dem Treiber-Board schon berücksichtigt und ohne Änderung möglich.

Beim TRS80 sind beide Möglichkeiten nicht gegeben. Auf DMA-Betrieb kann man verzichten. Die Änderung, die nötig ist, um das CPU-Board IM2-fähig zu machen, ist in <8> beschrieben. Die Signale MRD* und MWR* auf dem TRS80-Bus entsprechen nicht den Signalen RD* uns WR* des ECB-Bus. Dafür sind IN* und OUT* schon auf dem TRS80-Bus vorhanden. Alle nicht vorhandenen Signale müssen direkt auf dem CPU-Board abgegriffen werden.

Abb.5: Busweiche zur Verviefältigung des Systembus-Steckers.

Abb.5: Busweiche zur Verviefältigung des Systembus-Steckers.Wie man es auch dreht und wendet, jede Anordnung der Quetschstecker auf dem 50poligen Flachkabel führt dazu, daß die Ober- und Unterseite des GENIE-Bus auf den weitergebenden Steckern gegenüber dem Stecker für das CPU-Board vertauscht sind. Diese Schwierigkeit läßt sich nur dadurch beheben, daß die männlichen Zwischenstücke aus zwei Hälften bestehen, bei denen jeweils gegenüberliegende Streifen der Oberseite der einen Hälfte mit der Unterseite der anderen Hälfte und umgekehrt verbunden sind. Dazu verwendet man am besten kurze isolierte Steifen Schaltdraht. Eine andere Lösung besteht darin, daß der Stecker für das CPU-Board kein Quetschstecker sondern eine Ausführung zum Einlöten in Platinen (Apple-Slot) ist. An die Lötkontakte lassen sich dann die abisolierten Enden des Flachkabels in der richtigen Anordnung löten.

Literatur<1> Verbindend - Der ECB-Bus / Johannes Assenbaum / c't 12/85, 60-61

<2> Z80 CTC - Einsatz und Programmierung / Rolf Keller / c't 4/85, 92-94

<3> Interrupt-Priorit-Encoder und Vektorgenerator für IM2 mit dem Z80 CTC / H. Bernhardt / Info des GENIE/TRS80-User-Club Bremerhaven 12/85, 10-11

<4> Direkter Speicherzugriff: Schneller als die CPU - So arbeiten DMA-Controller-ICs / Rolf Keller / c't 8/85, 80-83

<5> Z80 DMA - schnell aber kompliziert / Rolf Keller / c't 12/85, 76-79

<6> Hardware-Umschaltung für den Betrieb von CP/M bei den Computern TRS80, GENIE 1 und 2 und Komtek 1 / H. Bernhardt / Info des GENIE/TRS80-User-Club Bremerhaven / Hardware-Sonderheft 11/85, 6-10

<7> Wie aus dem Komtek ein Computer wird / H. Bernhardt / Info des GENIE/TRS80-User-Club Bremerhaven / Hardware-Sonderheft 11/85, 1-5

<8> Interrupt Your 80 - With a hardware-mod, Your 80 is immune to rude interruptions / Dougla C. Fisher / 80 micro January 1983, 258-266